Construído originalmente a partir de único e simples circuito lógico CMOS que criado pelo próprio IMEC e um chip de memória DRAM comercial adquirida no mercado comum deram origem ao que poderá ser o CHIP 3D do Futuro. Os cientistas-pesquisadores tentaram reproduzir ao máximo os futuros chips voltados para aplicações móveis.

A meta era estabelecer os parâmetros de operação de um processador comercial encapsulado em um chip 3D, sobretudo com relação à dissipação de calor.

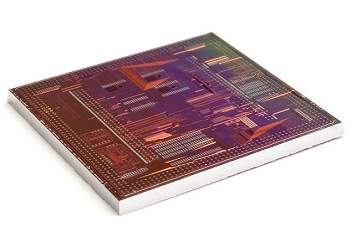

O instituto de pesquisas IMEC, da Bélgica, apresentou um chip 3D totalmente funcional que mescla processador e memória em um único circuito integrado.

Como o chip lógico utilizado não é um processador real, como os utilizados em notebooks e celulares, os pesquisadores inseriram aquecedores dentro da pilha 3D para simular a dissipação em condições realísticas de operação.

Pontos quentes

O chip 3D contém em sua estrutura um sistema de monitoramento do estresse termo-mecânico, para avaliar o impacto do calor dissipado, e um detector de descargas estáticas, que podem danificar o chip durante seu manuseio.

O chip 3D de demonstração mostrou que uma aplicação real exigirá uma espessura mínima de 50 micrômetros para o conjunto processador/memória para que seja possível lidar com os pontos mais quentes de cada um deles.

Devido à forte redução da capacidade de dissipação lateral, esses pontos quentes são ainda mais quentes do que nos chips 2D atuais e mais confinados, o que requer estratégias próprias de captura do calor e seu redirecionamento para o exterior do chip.

Outra conclusão importante é que o aquecimento do processador causa um aumento na temperatura da memória, diminuindo o tempo que os chips DRAM conseguem manter os dados.

Como a própria memória gera calor, e difunde esse calor pelo processador, o chip experimental mostrou que é inviável tentar isolar termicamente a memória e o processador.

Novas técnicas de resfriamento

“Estamos entusiasmados em atingir este marco importante. Este chip de teste, juntamente com nossas ferramentas de projeto 3D e nossos modelos termais representam um passo importante para a introdução da tecnologia 3D nos chips DRAM-sobre-lógica para aplicações móveis,” destacou Luc Van den Hove, do IMEC.

Embora os modelos termais tenham ajudado a identificar os pontos onde a dissipação de calor é mais crítica, será necessário desenvolver técnicas de resfriamento próprias para esses chips, capazes de coletar quantidades maiores de calor em determinados pontos.